シリコン量子ビット素子の特性が長い周期で変化する主な原因を特定

2024.12.08

PRESS RELEASE

研究成果発表

シリコン量子ビット素子の特性が長い周期で変化する主な原因を特定 量子コンピューターの安定動作を実現する基本素子の製造技術開発に前進

国立研究開発法人 産業技術総合研究所/学校法人 東京電機大学

ポイント

⚫シリコンFin型量子ビット素子における長周期の特性変化を解析

⚫絶縁膜/半導体界面における電子のトラップ現象が特性変化の原因であることを初めて特定

⚫量子コンピューターの利用可能時間を制限する各素子の状態診断・調整作業の軽減に前進

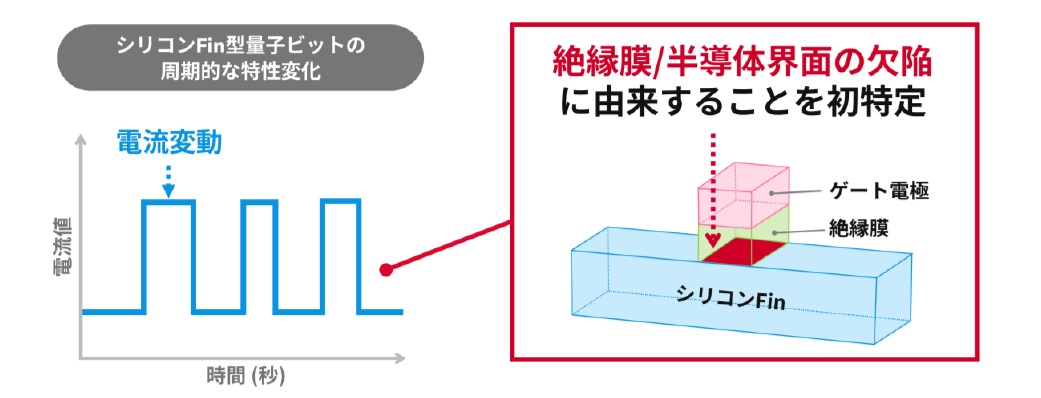

シリコンFin型量子ビットにおける長い周期での特性変化現象とその原因

シリコンFin型量子ビットにおける長い周期での特性変化現象とその原因

※原論文の図を改変したものを使用しています。

概 要

国立研究開発法人 産業技術総合研究所(以下「産総研」という)先端半導体研究センター 新原理シリコンデバイス研究チーム 岡 博史 主任研究員、浅井 栄大 主任研究員、加藤 公彦 主任研究員、森 貴洋 研究チーム長は、東京電機大学 森山 悟士 教授らと共同で、シリコン量子ビット素子の長周期の特性変化の原因を初めて特定しました。

量子コンピューターの基本素子である量子ビットは、数十秒や数時間以上の長い時間が経過した後に特性が変化し、時間がたつと元の特性に戻ることを繰り返す、といった長周期での特性変化が生じることが知られています。実運用されている量子コンピューターでも、時間単位での長周期の特性変化が観測されています。量子ビットの特性が変化した状態で計算を行うとエラーが生じるため、定期的な状態の診断と調整が必要です。調整作業には数時間を要する場合もあり、量子コンピューターの利用可能時間を制限しています。高集積量子コンピューターに向けて開発が進むシリコン量子ビット素子においても長周期の特性変化が生じますが、その原因は未解明でした。本研究では、シリコン型の中でも高集積化への期待が高いFin型量子ビット素子に生じる特性変化の原因が、絶縁膜/半導体界面の欠陥であることを世界で初めて特定しました。本成果により、シリコン量子コンピューターの安定動作に向けた量子ビット素子の製造技術開発に関する指針が得られました。この技術の詳細は2024年12月7日から米国サンフランシスコで開催される国際会議「IEEE International Electron Devices Meeting 2024」で発表されます。

下線部は【用語解説】参照

開発の社会的背景

量子コンピューターは量子重ね合わせ状態など量子力学的な現象を積極的に利用した計算機であり、量子化学計算や組み合わせ最適化問題など、社会的に重要な特定の問題を現代コンピューターより高速に計算できることが理論的に証明されています。量子コンピューターの基本素子である量子ビットには超伝導型やシリコン型などさまざまな方式がありますが、数十秒や数時間程度以上の長い時間が経過すると特性が変化し、さらに一定の時間がたつと元の特性に戻ることを繰り返す、といった長周期の特性変化が生じます。例えば、現在実運用されている超伝導型量子コンピューターでも時間単位での長周期の特性変化が観測されています。状態が変化したままで計算を行った場合、量子ビットが意図した状態にないため、計算結果にエラーが生じます。このエラーの発生を防ぐためには、特性変化の周期を考慮して定期的に状態を診断し、その調整作業を行う必要があります。この診断・調整作業は現在のところ、高い頻度かつ場合によっては数時間などの長時間を要するものであるため、ユーザーが量子コンピューターを利用できる時間を制限しています。

高集積量子コンピューターに向けて研究開発が盛んに進められているシリコン量子ビット素子においても、長い周期で電流-電圧特性が変化する現象が観測されています。シリコン型の中でも、Fin型(チャネルが立体的で魚のヒレに例えられる形状)のシリコン量子ビット素子は高集積化への期待が一段と高く、世界的に研究開発が進められているものの、長周期の特性変化の原因については未解明で、実験的な検証も十分に進んでいません。高度で実用的な量子計算を可能にする高集積量子コンピューターの安定な動作に向けて、シリコンFin型量子ビット素子における長周期特性変化の原因解明が待たれていました。

研究の経緯

産総研は、高集積量子コンピューターの実現に向けて、シリコン量子ビット素子およびその制御用エレクトロニクスとしてクライオCMOS回路・デバイスの研究開発に取り組んでいます。クライオCMOSデバイスの研究開発としては、これまでに極低温動作トランジスタのオン電流制限要因の理解(2022年国際会議VLSIシンポジウム発表)や回路の正確な設計に向けた極低温でのスイッチング特性の決定要因解明(2023年12月10日 産総研プレス発表)、極低温でのノイズ増大メカニズムの解明(2020年国際会議VLSIシンポジウム発表)、ノイズ発生源の特定(2023年6月12日 産総研プレス発表)など、世界をリードする研究成果を挙げてきました。

産総研 先端半導体研究センターは、シリコン量子コンピューターに向けた量子ビット素子の研究開発を進めており、今回、これまでに取り組んできたトランジスタの評価・解析手法を応用し、シリコンFin型量子ビット素子の長周期特性変化の主な原因を突き止めました。

なお、本研究開発は、文部科学省光・量子飛躍フラッグシッププログラム(Q-LEAP)「シリコン量子ビットによる量子計算機向け大規模集積回路の実現(2018~2027年度)」(JPMXS0118069228)による助成を受けています。

研究の内容

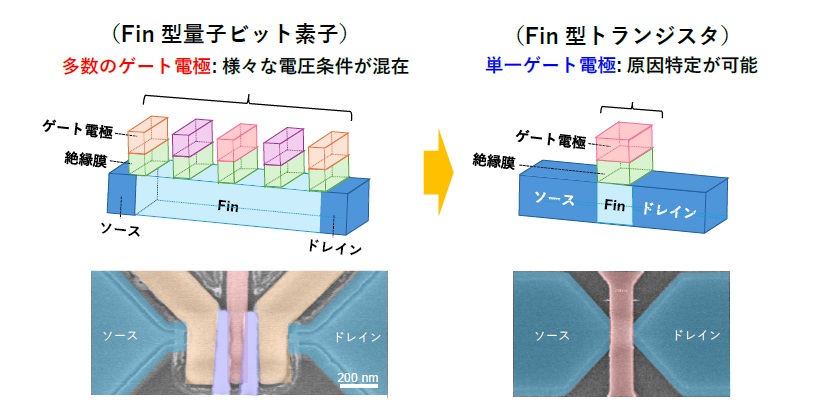

シリコンFin 型量子ビット素子では、数十秒程度の間隔で電流値が変化しては元に戻る、といった周期的な特性変化が観測されます(図1)。この周期的な変化が存在する状態で計算を行うとエラーを生じますが、原因の特定は容易ではありませんでした。シリコンFin 型量子ビット素子は、量子情報を担う電子をシリコン中に閉じ込める必要があるため、多数のゲート電極を利用します(図2 左図)。それぞれのゲート電極には異なる電圧を設定する必要があるため、 周期的な特性変化をもたらす要因がどのような電圧条件で生じるかの特定は、量子ビットの動作原理上、非常に困難でした。そこで、シリコンFin 型量子ビット素子と同じ材料・構造で、ゲート電極が一つしかない素子としてFin 型のトランジスタの利用を考案しました(図2 右図)。この場合、ゲート電圧条件を変えながら、電流値の時間変化の追跡が可能となります。今回、ゲート電極をFin の上部にのみ形成することで、Fin 型量子ビット素子と同じゲート構造としました。本研究ではこの方法で、周期的な特性変化の原因の特定に世界で初めて成功しました。

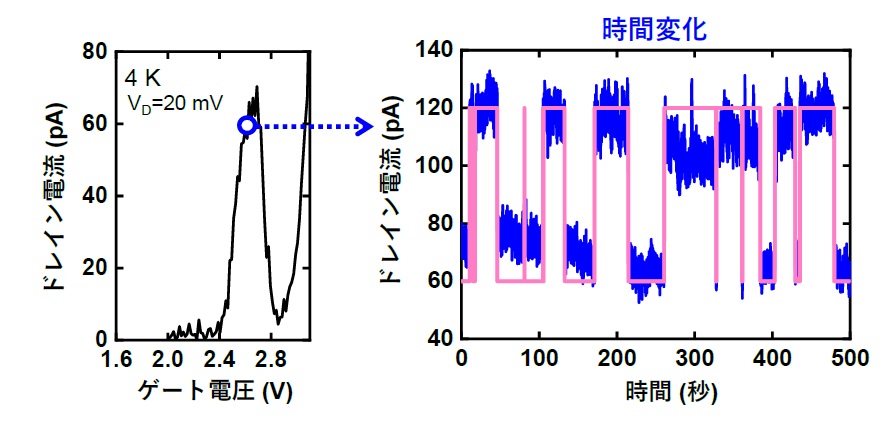

図1(左)シリコンFin 型量子ビット素子の電流-電圧特性と(右)ドレイン電流の時間変化

図1(左)シリコンFin 型量子ビット素子の電流-電圧特性と(右)ドレイン電流の時間変化

※原論文の図を改変したものを使用しています。

図2 Fin 型トランジスタを利用した長周期特性変化の原因特定

図2 Fin 型トランジスタを利用した長周期特性変化の原因特定

※原論文の図を改変したものを使用しています。

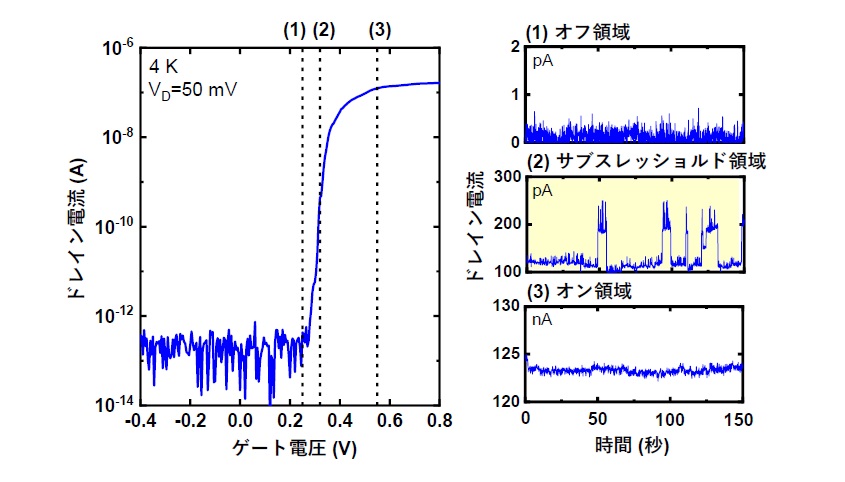

図3 左図は、作製したFin 型トランジスタの極低温(4 K)におけるドレイン電流-ゲート電圧特性を示しています。ゲート電圧を大きくすると、電流値が増大し、オフ領域からオン領域に移ります。オフ領域とオン領域の間の状態をサブスレッショルド領域と呼びます。各領域において一定の電圧下で、電流値の時間変化を追跡した結果が図3右図です。この結果から、オフ領域(図3 右図(1))とオン領域(図3 右図(3))では電流値が安定していますが、サブスレッショルド領域(図3 右図(2))の電圧条件においてのみ、電流値が数十秒間隔で増大と減少を繰り返す、周期的な変化が現れることがわかりました。これは、Fin 型量子ビット素子における周期的な特性変化が、サブスレッショルド領域の特定の電圧条件において生じていることを示唆しています。

図3(左)Fin 型トランジスタの電流-電圧特性と(右)各ゲート電圧における電流の時間変化

図3(左)Fin 型トランジスタの電流-電圧特性と(右)各ゲート電圧における電流の時間変化

※原論文の図を改変したものを使用しています。

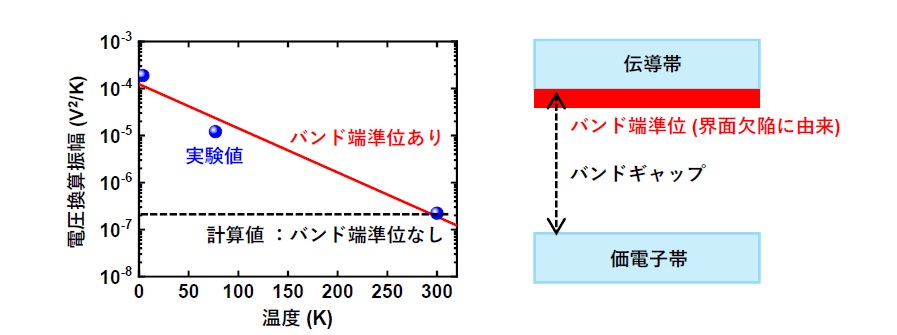

図4 周期的振幅の温度依存性とバンド端準位の概念図

図4 周期的振幅の温度依存性とバンド端準位の概念図

※原論文の図を改変したものを使用しています。

サブスレッショルド領域の電圧条件では、トランジスタの特性はバンドギャップの内部ではなく、バンドギャップの端(バンド端)に近い部分の影響を強く受けます。そのため、これらの結果は、バンド端に電流値の変化を引き起こす要因として、電子をトラップする準位が存在することを意味しています。実際に、周期的振幅を従来のモデルに基づいて計算すると実験値を再現できませんが、バンド端にトラップ準位が存在すると仮定すると、実験データとの一致が確認できました(図4)。これまでのわれわれの研究から、典型的なトランジスタの場合、バンド端のトラップ準位は絶縁膜と半導体の界面の欠陥に由来することがわかっています(2023年6月12日 産総研プレス発表)。この研究は、トランジスタにおけるスイッチング特性の劣化原因について明らかにしたもので、今回はこの知見が生かされました。この知見に基づくと、観測された長い周期での特性変化は、トランジスタのスイッチング特性の劣化と類似して、絶縁膜と半導体の界面で生じる電子のトラップ現象が原因であることがわかりました。これは、量子ビット素子の長周期特性変化の原因を初めて実験的に解明したものです。量子ビット素子そのものではなく、トランジスタに関する過去の研究があったからこそ明らかになった事実です。今回の研究から、周期的な特性変化の抑制には界面の品質が鍵であることが明らかになり、その向上がシリコン量子ビット素子の安定動作につながるという製造技術に関する指針が得られました。本知見により、シリコン量子コンピューターの研究開発の加速が期待されます。

今後の予定

今回得られた成果はシリコン量子ビットの安定動作に向けた素子製造技術の開発指針を与えるものであり、今後は、得られた知見に基づき、シリコンFin型量子ビット素子の試作と動作検証、界面の高品質化を含めたプロセス技術の開発を進めます。

学会情報

学会名:IEEE International Electron Devices Meeting 2024

タイトル:Origin of Long-period Electrical Instability in Silicon Fin-type Quantum Dots

著者:H. Oka, H. Asai, K. Kato, T. Inaba, S. Shitakata, S. Iizuka, Y. Chiashi, Y. Kobayashi, H. Yui, S. Nagano, S. Murakami, Y. Iba, M. Ogura, T. Nakayama, H. Koike, H. Fuketa, S. Moriyama, and T. Mori

用語解説

シリコン量子ビット素子

半導体材料であるシリコンを用いて製造される固体の量子ビット素子。シリコン量子ビットにはスピン量子ビットや電荷量子ビットの方式がある。

Fin型量子ビット素子

半導体微細加工プロセスにより製造されるシリコンが立体的で魚のヒレに例えられる形状をもつ量子ビット素子のこと。

超伝導型量子ビット素子

超伝導材料を用いて製造される固体の量子ビット素子。超伝導型量子ビットには磁束量子ビットやトランズモン量子ビットの方式がある。

ゲート電極

ゲート電極/絶縁膜/シリコン(Metal-oxide-semiconductor, MOS)構造により、ゲート電極に電圧を印加することでシリコン中の電子や正孔の密度を制御する役割をもつ。

トランジスタ

現代の電子回路において、信号を増幅したりスイッチングしたりするための素子。

トラップ準位

本稿でのトラップ準位は、バンドギャップ中に形成されるエネルギー準位を指し、電子や正孔の捕獲・放出の原因となる。絶縁膜/半導体界面の未結合手などの欠陥は、トラップ準位の成因となる。

スイッチング特性

トランジスタがオフ状態からオン状態になる際の電流の立ち上がり性能のこと。

機関情報

国立研究開発法人 産業技術総合研究所

https://www.aist.go.jp/

ブランディング・広報部 報道室 hodo-ml@aist.go.jp

学校法人 東京電機大学

https://www.dendai.ac.jp/

総務部 企画広報担当 keiei@jim.dendai.ac.jp

- 大学紹介

- 基本情報

- 学長挨拶

- 顧問学長対談

- 副学長・学部長等 役職者

- 建学の精神と教育・研究理念

- 東京電機大学大学院・大学の3つのポリシー

- 大学のあゆみ

- 大学の取り組み

- 情報公開

- 認証評価、自己点検・評価

- ホームカミングデー

- 東京電機大学が求める教員像

- 教育関係附置施設

- キャンパス紹介

- 東京電機大学大学のアセスメント・ポリシー

- 学園紹介

- 学校法人東京電機大学概要

- 理事長挨拶

- 理事・監事

- 評議員

- 事業・財務情報

- ガバナンス

- 学園創立100周年宣言

- 学園広報物

- TDUコメンテーター教員紹介

- 学園へのご寄付

- 学校法人東京電機大学が求める事務・技術職員像

- 学園創立110周年記念事業

- 系列校・関連機関

- 寄附行為等

- 危機管理

- 新型コロナウイルス感染者状況

- 学校法人東京電機大学中期計画~TDU Vision2028~

- 学部

- システムデザイン工学部

- 未来科学部

- 工学部

- 工学部第二部

- 理工学部

- 大学院

- 大学院での学び

- 先端科学技術研究科

- システムデザイン工学研究科

- 未来科学研究科

- 工学研究科

- 理工学研究科

- 入試・オープンキャンパス

- 大学入試

- 大学院入試

- インターネット出願/マイページ

- 入学者選抜要項

- 入試結果

- オープンキャンパス2025

- オンライン個別相談会

- 進学相談会

- キャンパス見学会

- キャンパス自由見学

- キャンパス見学

- メールマガジン

- ざっくりまとめました! 東京電機大学の7つのこと

- 【一般選抜】東京千住キャンパス試験会場案内(ストリートビュー)

- 1分で電大が分かる!ショート動画

- 受験生への応援メッセージ

- キャリアプログラム

- 学内就職サイト

- 就職支援

- 資格取得・教員免許

- 公開講座

- 履修証明プログラム

- 実践知教育

- 留学・国際交流

- 本学へ留学希望の方

- 本学へ留学希望の方(最新TOPICS)

- 海外に留学希望の方

- 海外に留学希望の方(最新TOPICS)

- 海外留学動画(学内者専用)

- 国際センター

- TDU International Workshop

- International Workshop

- スチューデントアンバサダー

- 国内でできる国際交流

- 在留期間更新許可申請

- 学生生活

- 学生要覧

- 履修の手引き

- 教職課程

- シラバス・時間割

- 年間予定

- 学習サポートセンター

- 学生アドバイザー

- 障害のある学生への支援

- その他授業関係

- 学費

- 奨学金

- 教育ローン・短期貸与金制度

- 保険制度・経費補助

- 証明書発行・事務窓口

- 学生相談室・健康相談室

- 休学・退学などについて

- クラブ・サークル活動

- 学生食堂と売店

- 車両通学

- ⾼等教育の修学支援新制度(授業料等減免・給付型奨学金の支援)について

- 東京電機大学後援会

- 教育訓練給付制度